廣東作為中國經濟發展的重要省份,其面皮市場在預包裝食品領域占據著重要地位。面皮作為一種傳統且便捷的食品,在廣東乃至全國都擁有廣泛的消費群體。本文將詳細介紹廣東面皮的市場現狀,包括主要品牌廠家、預包裝食品批發渠道以及價格報價趨勢,幫助讀者全面了解這一領域。

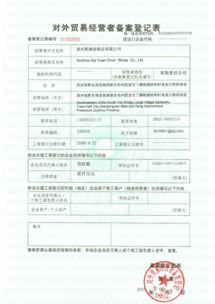

廣東的面皮市場品牌眾多,既有本地知名廠家,也有全國性大品牌入駐。例如,像“廣州老字號面點廠”和“深圳速食食品有限公司”這樣的本地企業,專注于生產高質量的面皮產品,注重傳統工藝與現代技術的結合。這些廠家通常提供多種口味和規格的預包裝面皮,如寬面皮、細面皮、以及添加蔬菜或肉類的特色產品,以滿足不同消費者的需求。在批發渠道方面,廣東的預包裝食品批發市場非常發達,主要集中在廣州、深圳等大城市的食品批發城,如廣州江南果蔬批發市場和深圳華南城國際食品交易中心。這些市場提供一站式采購服務,批發商可以直接與廠家合作,獲得優惠的批發價格。隨著電商的興起,許多廠家也通過阿里巴巴、京東等平臺開展線上批發業務,方便全國各地的客戶訂購。

關于面皮的價格報價,廣東市場的價格因品牌、規格和采購量而異。一般來說,普通預包裝面皮的批發價在每500克5元至15元人民幣之間,高端品牌或有機面皮可能達到20元以上。例如,基礎款的全麥面皮批發價約為8元/500克,而添加了海鮮或特色配料的創新產品可能報價在12-18元/500克。批發商通常根據采購量提供階梯式折扣,如一次性采購100箱以上可享受5%-10%的優惠。值得注意的是,價格還受原材料成本、運輸費用和季節因素影響,例如小麥價格波動可能導致面皮報價在短期內調整。建議批發商定期與廠家溝通,獲取最新報價,并關注市場動態以優化采購策略。

總體而言,廣東的面皮市場充滿活力,品牌廠家不斷創新產品,預包裝食品批發渠道日益多元化。對于想進入這一領域的商家來說,選擇合適的品牌和批發伙伴至關重要。通過深入了解價格趨勢和市場需求,可以抓住商機,實現可持續發展。如果您需要更詳細的信息,建議直接聯系相關廠家或訪問專業食品展會獲取一手資料。